CML社 CMX940のご紹介

本コラムの構成

■はじめに

■境界スプリアスの回避と低ノイズの両立

■VCOキャリブレーション時間

■はじめに

優れたシンセサイザーの設計には、ターゲットとするアプリケーションにとって相反する要件でバランスさせる必要があります。 CML社 CMX940 High Performance RF Synthesizerは、優れた低ノイズ性能と低消費電力を両立しており、新たにリリースされたアプリケーションノート「Application Note CMX940 PLL Fast Lock Method」にてCMX940での高速なスイッチングタイムを実証しています。

■境界スプリアスの回避と低ノイズの両立

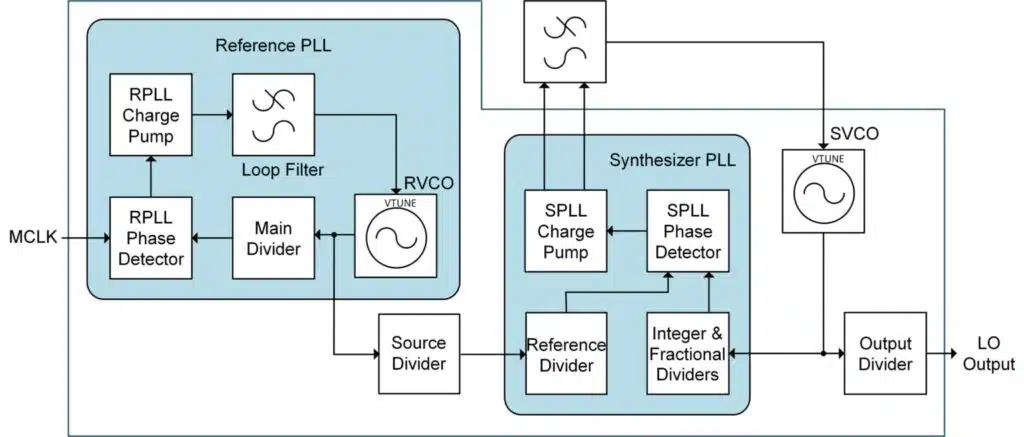

境界スプリアスを回避しながら、-125dBc/Hzというとても低いin-loopノイズを達成するため、CMLでは、新しい dual PLL アーキテクチャを採用しました。このアーキテクチャは、シンセサイザーPLLに加えて、超低ノイズのリファレンスPLLを使用します。このアーキテクチャによって、低ノイズと49〜2040MHzの広帯域動作を両立しています。

CMX940 Dual PLL Architecture

■VCOキャリブレーション時間

通常より小さな実装設計を容易にするため、通常はオンチップVCOを使用します。これらのVCOは、サポートする全周波数帯域でより良い精度を確保するためにon-chip auto-calibration機能を持っています。

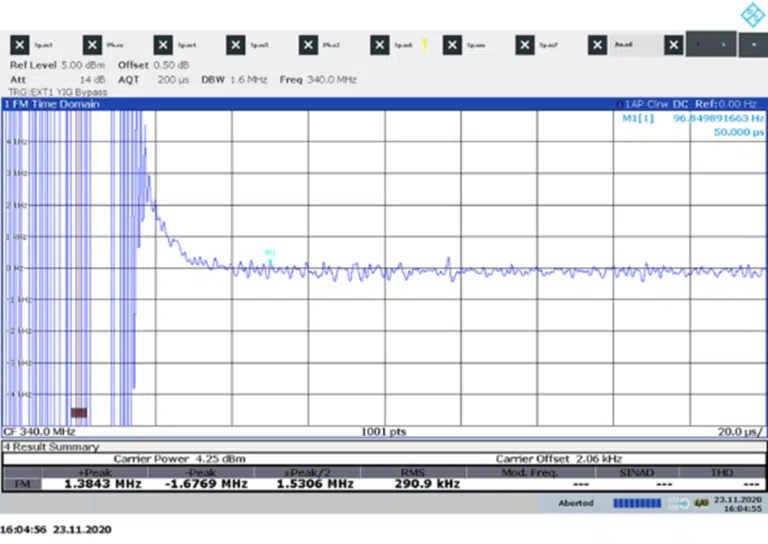

on-chip auto-calibration機能は、他の形式のキャリブレーション方法と同様、目的の結果を得るにはある程度の時間を必要とします 。通常は、PLLがキャリブレーションとロックし、安定し正確な周波数を出力します。しかし、場合によってはこの過程における時間によって、周波数の高速な変更を必要とする特定のアプリケーションから、CMX940が除外されてしまうことがあります。例えば、周波数ポッピングを使うアプリケーションでは、安定している現在の周波数から別の周波数へ高速にジャンプできるシンセサイザーが要求されます。(わずか数100usのようなことも、珍しくありません)

CML社では、このようなリクエストに対応するために、今回のアプリケーションノートをリリースしました。

(CMX940 PLL Fast Lock Method https://cmlmicro.com/Content/Product%20Downloads/RF%20Building%20Blocks/CMX940-PLL-Fast-Tuning-Method_Iss_2.pdf)

本アプリケーションノートでは、それぞれのVCOに直接書き込むことが可能な既知のキャリブレーションパラメータを使って、キャリブレーションされたVCOを更新する機能について説明しています。

さらに、既知のキャリブレーションパラメータをon-the-flyで変更する機能もハイライトしています。この機能は、動作中にVCO周波数がドリフトした場合(例えば温度変化が原因でドリフトが発生する場合)に便利な機能です。

50us未満のスイッチング時間を達成するために、周波数を切り替える方法を説明しテストする例を示します。この例でのPE0003+EV9400 で使用可能なスクリプトも、この方法がいかに効果的であるかを示します。

このように、CMX940は、低ノイズ、低消費電力、高速な周波数切り替えを必要とするアプリケーションに最適な妥協点を提供することを示すことができます。

CMX940 PLL Fast Lock Method アプリケーションノートは、CMX940 製品ページ( https://www.cmlmicro.com/

◆【Webマガジン Vol.43- Sep., 2021】Column: CML社 CMX940(VCO PLL IC)の評価ボードEV9400での最適な周波数設定方法

CML社製品に関するご質問やご要望等ございましたら、お問い合わせフォームより、お気軽にお問い合わせください。

この記事の監修者

コーンズテクノロジー編集部

コーンズテクノロジーでは先進的な製品・技術を日本産業界へ紹介する技術専門商社として、通信計測・自動車・防衛セキュリティ・電子機器装置・航空宇宙・産業機械といった技術分野のお役立ち情報を紹介しています。